#### Module - 03

Op Amp as Non-Linear Circuit

Operational amplifiers are widely used in circuits in which the output is switched between the tree and the solution levels. Positive feed back is employed in these circuits.

$$\begin{aligned} \text{senerally}, & + \text{Vsot} \simeq (\text{V}_{cc} - 1\text{V}) \\ & - \text{Vsat} \simeq (-\text{V}_{EE} + 1\text{V}) \end{aligned}$$

The IV difference may change from Op-amp to op-amp. For very small change in input voltage, the op-amp Output switches from +Vsat to -Vsat.

# Input Voltage Range:

In linear applications, -ve feedback keeps the operation input terminal, closely equal. In switching applications, the dc voltage level at one input terminal is different from that at the other input terminal. The switching application normally employ the feedback to provide a subtaintial voltage difference between the two input terminals. This ensures that o/p is saturated at either a the or -ve voltage level. so, in switching applications, there is normally a differential voltage of the op-amp input terminal.

The minimum differential voltage required to produce output saturation is given by :-

$V_i(diff) \simeq \frac{V_{cc}}{M_{min}}$ , where  $M_{min} \simeq \frac{M_{in}}{M_{min}}$  op Omp.

For 741 op-amp, Mmin  $\approx 50,000$ If a ±15V supply is used, Vicdiff) =  $\frac{\pm 15V}{50,000}$  =  $\pm 300 \text{ av}$

Most op-amp can accept a differential input voltage equal to twice the supply voltage. The op-amp input stage may be domaged if this maximum is exceeded. For eq: , with a ±15v supply, the maximum differential input should not exceed 30v.

Op-amp as comparator

A comparator is a circuit which compares a signal voltage applied at one i/p of an op-amp with a known reference voltage at the other end, and produces either a high or a low output voltage, depending on which i/p is higher.

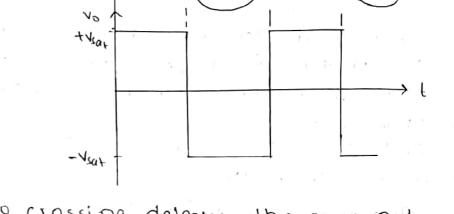

## Zero Crossing Detector (200)

The Important application of comparator is zero crossing detector.

٧ı

- The types of ZCD aver-

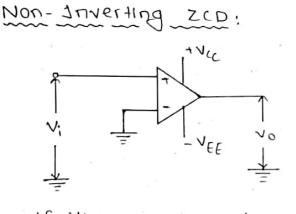

- \* Non- inverting ZCD

- \* Inverting ZCD

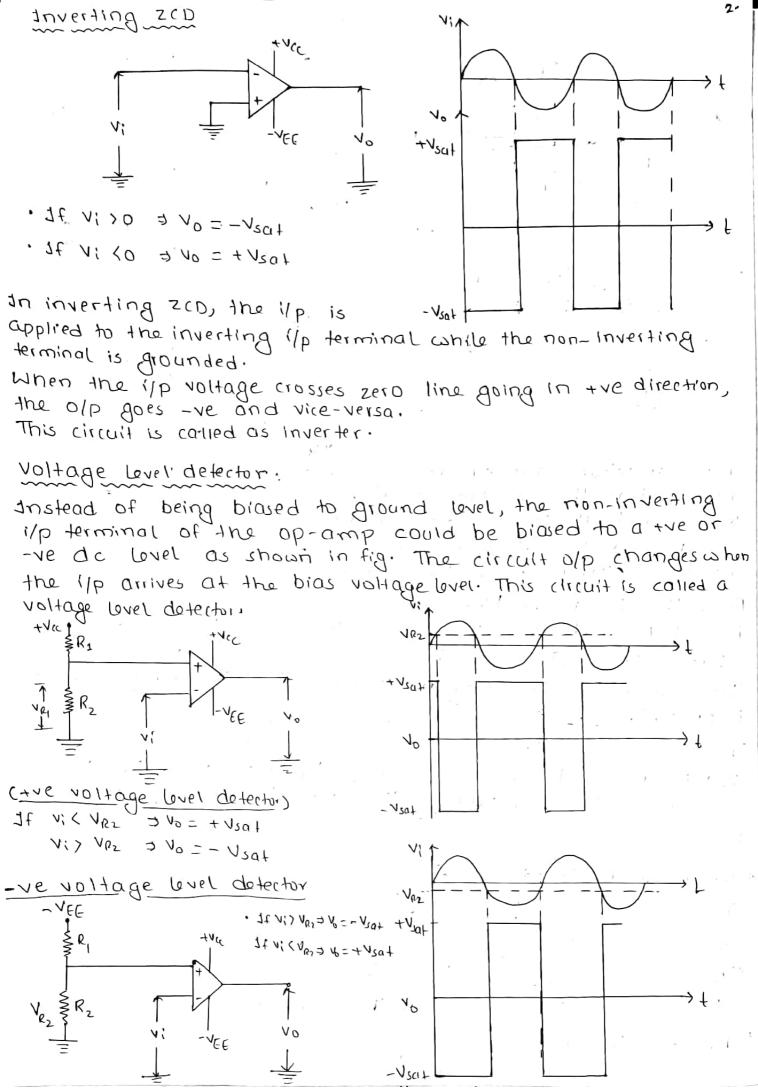

- \* capacitor coupled ZCD.

- · 1f V; > 0 → Vo= + Vsat

- · 7t Ni (0 = No = Not

In a non-inverting zero crossing detector, the op-amp is used in open loop mode. Inverting terminal is grounded and input is applied to the non-inverting terminal. When the i/p is below ground level, the O/p is saturated at its -ve extreme. When the i/p goes above ground level by 300 w, the O/p immediety switches to the saturation level. Each time the i/p voltage crosses zero level, the O/p switches from one saturation level to the othern since, the O/p moves in a the direction when the i/p crosses zero from -ve to the circuit is said to be non-interting zco. Regardless of the i/p waveshape, the o/p is always a rectangular wave form.

Scanned with CamScanner

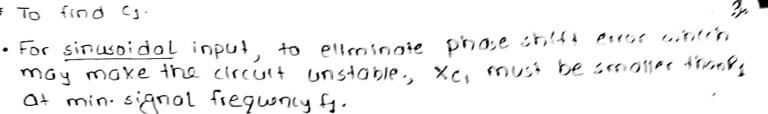

+ To find (1.

$$X_{c_1} = \frac{1}{20} R_1 \Rightarrow C_1 = \frac{1}{2\pi f_1 (P_1/20)}$$

. When a <u>square</u> wave is applied as an i/p to the caparitor coupled crossing detector, the waveform can develop tilt at op-amp input terminal as shown. As long as the olp is constant at saturation level, till is insignificant. In such case, to determine (1, first time t is measured for

acceptable filt in Vx.

$$I_{1} = \frac{V_{i}}{R_{1}}$$

$$C_{1} = \frac{I_{1}t}{\Omega V} , t = \frac{1}{2t}$$

· If v; is square wore • Let,  $R_2 = 1 M \Lambda$ choose G= 0.14F . · Find I2 & calculote R3 CI = IIt => Find I, DV=JV  $R_2 = \frac{V_{R2}}{J_2} = \frac{V_{G} - V_B}{J_2}$  $\therefore I_2 = \frac{V(r - VB}{P_2}$ I, = Vi/R, :. R1 = V:/31 Find  $P_3$ ,  $R_3 = \frac{VB}{J_2}$ · If V: is sinuaso; dol wave  $X_{C_1} = \frac{1}{20} R_1$ Choose (1=0.14F

O. A capacitor coupled zero crossing detector is to handle 1 KHZ square wave 11p with a peak to peak amplitude of 6 v. Désign à suitable circuit using à 741 Op amp with a ± 12V supply.

5017: CDIOW circuit diagram and waveform) Let, 72 = 100 ] B max = 100 × 5000A = 50 UA.

Let,

$$V_{B} = 0.1V$$

$V_{R_{2}} = V_{CC} - V_{B} = 12V - 0.1V = 11.9V$

$R_{2} = V_{R_{2}} = \frac{11.9}{50 \times 10^{6}} = 238 \text{ km} \approx 220 \text{ km}$

$V_{R_{3}} = V_{B} = 0.1V$

$R_{3} = \frac{V_{R_{3}}}{T_{2}} = \frac{0.1}{50 \times 16^{6}} = 216\pi \approx 4.8 \text{ km}$

$R_{3} = \frac{V_{R_{3}}}{T_{2}} = \frac{0.1 \times 0.7}{500 \times 16^{9}} = 140 \text{ km} \approx 120 \text{ km}$

$V_{1}(peok) = \frac{6V}{2} = 3V$

$V_{1}(peok) = \frac{6V}{2} = 3V$

$\frac{5quare conve:}{T_{1}} = \frac{3}{120 \times 10^{3}} = 25 \text{ mA}$

$t = \frac{1}{2f} = \frac{1}{2 \times 1 \times 10^{3}} = 500 \text{ ms}$

$C_{1} = \frac{T_{1}t}{\Delta V} = \frac{25 \times 10^{6} \times 500 \times 10^{6}}{4} = 0.0125 \text{ mF} \approx 0.015 \text{ m}$

(D) A capacitor coupled ZCD is to provide an o/p voltage approx. ±17V when a BicHZ, with ±2V square wave 1/p is applied. Design a suitable detector using bipolor op omp.

$$\frac{501^{n}}{4} + \frac{V_{301}}{2} = + \frac{1}{2} \frac{1}{2} = \frac{3}{2} \frac{1}{2} = \frac{3}{2} \frac{1}{2} = \frac{1}{2} \frac{1}{2} \frac{1}{2} = \frac{1}{2} \frac{1}{2} \frac{1}{3} \frac{1}{2} = \frac{1}{2} \frac{1}{3} \frac{1}{2} \frac{1}{3} \frac{1}{3} \frac{1}{3} \frac{1}{3} = \frac{1}{2} \frac{1}{3} \frac{1}{3$$

$$\begin{array}{rcl} \hline BJFET & R_2 &= 1 \, \text{M} \, \text{M} \\ \hline T_2 &= & \frac{\sqrt{R_2}}{R_2} = & \frac{\sqrt{(c-\sqrt{B})}}{R_2} = & \frac{(18-0.1)}{10^6} = & \frac{1.79 \times 16^5 \, \text{A}}{R_3} \\ \hline R_3 &= & \frac{\sqrt{R_3}}{T_2} = & \frac{\sqrt{B}}{T_1} = & 5-5 \, \text{k.s.} & \approx 5.6 \, \text{k.s.} \\ \hline R_3 &= & 0.1 \, \text{uf} & , & \frac{\sqrt{(c-\sqrt{B})}}{R_1} & R_1 = & 3.3 \, \text{k.s.} \\ \hline Chrosse, C_1 &= & 0.1 \, \text{uf} & , & \frac{\sqrt{(c-\sqrt{B})}}{R_1} & R_1 = & 3.3 \, \text{k.s.} \end{array}$$

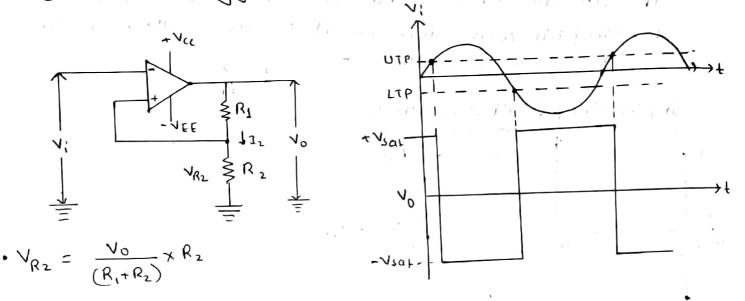

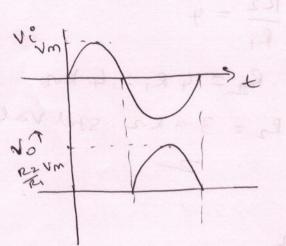

Inverting schmitt Trigger circuit

In a basic comparator, a feed back is not used and the op-Amp is used in the open loop mode. As open loop gain of Opamp is lorge, very small noise voltages can cause triggering of the comparator, to change its state. This may cause lot of problems in the applications of comparator as ZCD. Such unwanted noises cause the output to jump between high and low states. The comparator circuit used to avoid such unwanted triggering is called Regenerative comparator or schmitt trigger, which basically uses the feedback.

• If  $N_i < V_{R_2} \Rightarrow V_0 = + V_{sat}$

VR2 = + Vsat xR2 -> UTP (Upper triggering point)

• 14 Vi  $\langle VR_2 \Rightarrow V_0 = -Vsat$  $VR_2 = -\frac{Vsat}{R_1 + R_2} \rightarrow LTP$  (Lower triggering point)

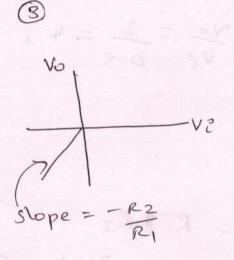

The basic circuit of inverting schmitt trigger is shown above. The i/p is applied to the inverting terminal and the feedback is provided. The voltage at non inverting ilp is  $V_{R_2} = \frac{V_0}{R_1 + R_2} \times R_2$ when the o/p voltage is saturated in the direction at tNsat,  $V_{R_2}$  is a positive quantity. When the olp is at -Vsat,  $V_{R_2}$  is negative.

Scanned with CamScanner

4.

The o/p switch from the tve soturation level to the -ve saturation level only when the inverting i/p terminal is raised above the voltage at non-inverting input terminal (VR2).

+V<sub>R2</sub> is for +ve saturation when Vo= +Vsat and is called UTP (Upper Threshold point) -V<sub>R2</sub> is for -ve saturation when Vo=-Vsal and is called LTP (Lower Threshold point) The o/p switches from +ve to -ve when the Yp voltage reaches UTP and from -ve to +ve when

the i/p fails to LTP. So, the O/p is always a rectangular waveform. So, it is also called sine to square wave converter.

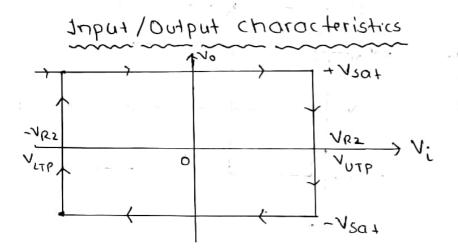

Typicol I/o characteristics of on op amp inverting schmitt trigger is shown above.

Initially with o/p at +Vsat and i/p at zero, when vi is raised to UTP, the o/p switches from +Vsat to-Vsat. Any further increase in Vi obove UTP maintains the o/p at -Vsat. When the i/p is being reduced from ' UTP to the LTP, the o/p remains at -Vsat.

When Vi equals the LTP, the old rapidally switches from -Nsat to +Nsat · Now any further decrease in Ni below the LTP, maintains the old voltage of + Vsat -

The voltage difference between the upper and solutions is referred to as hydreess.

V<sub>H</sub> = UTP-LTP

$$= \frac{+N_{SAL}}{R_1 + R_2} \times R_2 - \left[ \frac{-V_{SAL}}{R_1 + R_2} \times R_2 \right]$$

When V<sub>1</sub> < LTP, V<sub>0</sub> = +V\_{SAL}

V<sub>1</sub> > UTP = V<sub>0</sub> = +V\_{SAL}

V<sub>1</sub> > UTP = V<sub>0</sub> = -V\_{SAL}

UTP = V<sub>0</sub> < UTP = V<sub>0</sub> = Previous state.

Design steps:

Let, the current through R<sub>1</sub> and R<sub>2</sub> is I<sub>2</sub>.

I<sub>2</sub> = 100 J<sub>B</sub>max

R<sub>1</sub> =  $\frac{V_0 - Triggering voltage}{I_2}$

R<sub>1</sub> =  $\frac{V_0 - Triggering voltage}{I_2}$

R<sub>2</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• choose R<sub>1</sub> = 1 m.

• Find J<sub>2</sub>

I<sub>2</sub> =  $\frac{V_0 - Triggering voltage}{I_2}$

Biffer:

• choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• Choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• Choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• Choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• Choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• Choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>3</sub> =  $\frac{Triggering voltage}{I_2}$

Biffer:

• Choose R<sub>1</sub> = 1 m.

• Find R<sub>2</sub>

R<sub>4</sub> =  $\frac{T_2}{I_2}$  =  $\frac{2V}{I_2}$  =

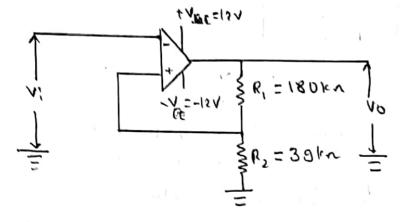

$V_{R_1} = V_{0_{SQ_1}} - V_{R_2} = (12 - 1) - 2 = 9V$  $R_1 = \frac{V_{R_1}}{J_2} = 180 \text{ km} = 180 \text{ km}$

$$R_{1} = 1M\Lambda$$

$$I_{2} = \frac{V_{0} - Triggering vollage}{R_{1}} = \frac{14 - 2}{1 \times 10^{6}} = 94A$$

$$R_{2} = \frac{Triggering vollage}{I_{2}} = \frac{2}{9 \times 10^{6}} = 222 \ln \Lambda \approx 220 \, \mathrm{kn}$$

Q. An inverting schmitt trigger is to be designed with triggering voltage ±0.5v and to produce the olp = ±11v. Useral op Amp.

$$SOIN: J_2 = (00]Bmax = 504A$$

$$R_2 = \frac{T_{12}gering vollage}{J_2} = \frac{0.5}{50 \times 10^6} = 10 \text{ km}$$

$$R_1 = \frac{11 - 0.5}{50 \times 10^{-6}} = 210 \approx 180 \text{ km}$$

a. Design an inv. schmidt trigger to have driggering points of tax with a supply of ±150

$$SOIM: J_2 = 100 J_{Bmax} = 504A$$

$$R_2 = \frac{4}{50 \times 10^6} = 80 Kn$$

$$R_1 = \frac{14 - 4}{50 \times 10^6} = 200 Kn$$

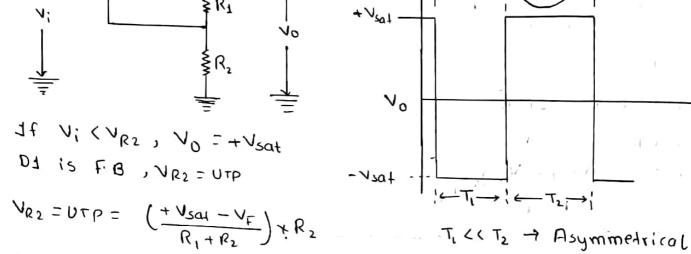

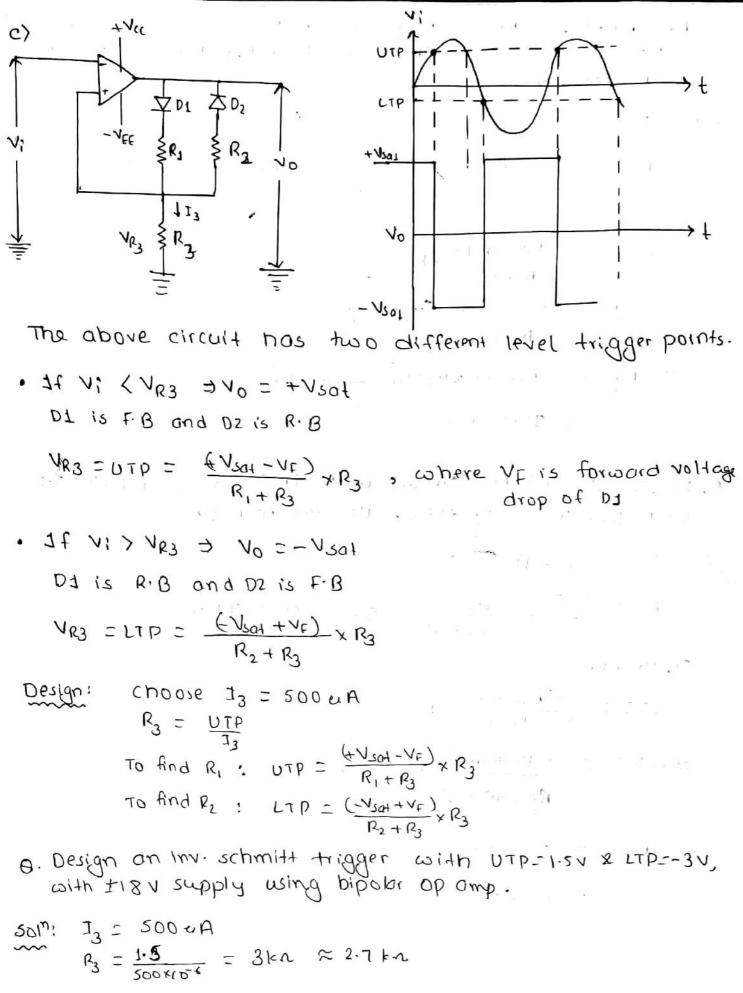

Adjusting Triggering points 6. Inverting schmitt trigger circuits with different UIP & LIP

Asymmetrical schmitt Trigger

立り

≩R1

•  $V_{R_2} = UTP = \left(\frac{+V_{Sal} - V_F}{R_1 + R_2}\right) + R_2$ Vf -> Diode voltage.

a>

Jf V; > VR2, No =- Nsat D1 is R.B, VR2 = O (LTP)

In the above circuit, UTP is combined with a zero voltage LTP. When the olp is the Dit is Forward blased and UTP is the drop across R2. When the O/p is -ve, D1 is reverse biased, only the op-omp input bias current flows in Rz and the optimp non-inverting ilp terminal is held close to ground level. The o/p will go the once again when the ilp voltage is reduced below ground level. The diode D1 must be selected to have a maximum reverse voltage greater than the circuit supply voltage. It's maximum reverse recovery time (trr) should be much smaller than the min pulse width of the ilp signal. . t<sub>rr</sub> ≤ Min. pulse width

- >6 Design: 741: Jui, J<sub>2</sub> = 500 4 A ( To handle diode forward (user, 12 = 5000A)  $\mathbf{R}_2 = \frac{\mathbf{UTP}}{\mathbf{J}_2}$ · To find R1, 5  $UTP = \left(\frac{+V_{sal} - V_{F}}{R_{s} + R_{s}}\right) R_{2}$ BIFET: · choose R, = IMA · Find R2.  $UTP = \frac{\left( +V_{sat} - V_{F} \right)}{R_{1} + R_{2}} \times R_{2}$ +1/10 Ьγ \*\* 古山 LTP LIP VO tVsat  $V_{R_2}$   $R_2$ No . 14 V; > VR2, VO = - Vsot - A201 DA is F.B, VR2 = LTP  $-V_{R2} = \frac{(-V_{S01} + V_{F})}{R_{1} + R_{2}} \times R_{2}$ Design : J2 = 500 4A  $R_2 = \frac{LTP}{T}$ · If V: < VR2, VO-+ VSAL Find R, DI IS R.B, VR2 = 0

a An inverting schmidt trigger is to LTP=OV. Design a suitable circuit have UTPEIV and using bipolor opamp with supply vollage of #154. . .

$$\frac{3017}{R_2} = \frac{1}{12} = \frac{1}{500 \times 10^6} = 2 \times n \propto 1.8 \times n$$

$$R_2 = \frac{1}{12} = \frac{1}{500 \times 10^6} = 2 \times n \approx 1.8 \times n$$

$$To find R_1,$$

$$\Rightarrow I = \frac{(14-0.7)}{R_1+R_2} \times R_2 \Rightarrow I = \frac{(14-0.7)}{(R_1+1.8\times10^3)} \times 1.8\times10^3 = (14-0.7)\times1.8\times10^3 - 1.8\times10^3 = 12.14\times10^3$$

Q. Design a suitable circuit with UTP=ON and LTP=2.5V with power supply ±18V. Use 741 0p Amp.

$$SO(n)! \quad J_2 = SOO \cdot u A$$

$$R_2 = \frac{LTP}{J_2} = \frac{2 \cdot 5}{500 \times 10^6} = 5 k \Lambda \approx 4 \cdot 7 k \Lambda$$

$$To find R_{1,1}$$

$$LTP = \left(\frac{-V_{SOU} + V_{1,1}}{R_1 + R_1}\right) \times R_2$$

$$LTP = \left(\frac{-3241}{R_1 + R_2}\right) \times R_2$$

= -2.5 =  $\left(\frac{-17 + 0.7}{R_1 + 4.7}\right) \times 4.7 \times 10^3$

$R_1 + 4.7 \times 10^3$

$$\Rightarrow$$

R<sub>1</sub> = 25.84 km

$\approx 22 km$

1 ×1 ×1 ×1 ×1 ×1 ×1 ×1 ×1

### Scanned with CamScanner

č. I

12 12 4

$$UTP = \left(\frac{+V_{SQ1} - V_F}{R_1 + R_3}\right) R_3 \implies R_1 = 26.69 kn \approx 27 kn$$

$$LTP = \left(\frac{-V_{SQ1} + V_F}{R_2 + R_3}\right) R_3 \implies R_2 = 15.97 kn \approx 12 kn$$

The circuit diagram of Amv using schmitt trigger is shown in figure. The op-amp with resistors  $R_2$  and  $R_3$  forms an inverting schmitt trigger circuit. The ilp voltage to schmitt trigger is the voltage across capacitor  $C_1$  which is charged from the Op-amp O/p via resistor  $R_1$ . When the power is turned ON, the Output outomatically swing either to the to the or to -Nsot. Since, these are the only stable states allowed by the schmitt trigger. Let, the circuit Olp be at the saturation level, current flows into the capacitor, charging 14 until the Nor reaches the UTP of the schmitt trigger. The Olp than rapidly switches to the -ne saturation level. Now, capacitor starts discharging Nia R1 and capacitor charges with opposite polarity. This continues luntil Nor teaches LTP, then the Olp rapidly switches back to the saturation level, and cycle starts again.

# Design:

• The minimum current through R<sub>1</sub> is selected to be much lorger than the op-amp input bias current

$I_1 = 100 J_{Bmax}$

- $R_1 = \frac{|V_0| UTP}{I_1}$

- . Once R, is determined, (1 can be calculated from the capacitor charging equation.

If schmitt trigger UTP and LTP are selected to be much smaller than op-amp o/p voltage, the voltage across R1 will not change much.

consequently, the capacitor charging current (II) can be a constant & from which (I can be obtained.

$C_1 = \frac{I_1 \times I}{\Delta V}$ ,  $\Delta V = UTP - LTP$  UTP = + 0.5VLTP = -0.5V

Let, I3 = 100 IB ma,

$$R_{3} = \frac{UTP}{I_{3}}$$

$$R_{2} = \frac{|V_{0}| - UTP}{I_{3}}$$

### BIFET

The capacitance of (, should be first selected to be much lorger than stray capacitonce.

- · Choose C1 = 0.1 4F.

- Find I,  $t_1 = \frac{c_1 \Delta v}{t_1}$ •  $R_1 = \frac{|V_0| - UTP}{T_1}$

- Choose  $R_2 = 1MR$ • Find I3,  $I_3 = \frac{|V_0| - UTP}{R_2}$

- $R_3 = UTP I_3$

- Q. Using a BIFET op amp, design on Amv to have a ±9V o/p with frequency of 1 kHz.

- Sol<sup>n</sup>: For  $V_0 = \pm 9V$   $V_{CC} = \pm V_0 + 1 = \pm 9V + 1 = \pm 10V$   $Select_0 UTP = LTP = 0.5V$   $Let_1, R_2 = \pm Mn$   $J_3 = \frac{|V_0| - UTP}{R_2} = \frac{9V - 0.5V}{\pm mn} = 8.5UR$   $R_3 = \frac{UTP}{R_2} = \frac{0.5V}{\pm mn} = 59kn \approx 56 kn$   $k_0 = \frac{1}{2f} = \frac{1}{2N_0^3} = 500us$   $J_1 = \frac{1}{2f} = \frac{1}{2N_0^3} = 500us$   $J_1 = \frac{1}{2f} = \frac{1}{2N_0^3} = 200UR$  $R_3 = \frac{V_0 - UTP}{J_1} = 47.5kn \approx 39 kn$

g.

G. Design an Oppamp Arry to have an old figuraty of 400 Hz

Use a Tall oppamp with a supply of ±18v.

$$f = 400 \text{ Hz}, T = 2.5 \text{ ms}, t_1 = 1.75 \text{ ms}$$

Solid J. J. = 100 J<sub>Bmax</sub> = 50 UA

$R_1 = \frac{17 - 0.5}{50 \text{ H}6^2} = 330 \text{ KL}$

$C_1 = \frac{1.4}{4v} = \frac{50 \text{ K}16^4 \times 1.25 \times 16^3}{1} = 62.5 \text{ mF} = 0.06 \text{ G}F$

$J_3 = 1007_{Bmax} = 50 \text{ G}A$

$R_3 = \frac{0.5}{50 \text{ K}16^2} = 10 \text{ KL}$

$R_2 = \frac{17 - 0.5}{50 \text{ K}16^2} = 330 \text{ KL}$

$R_3 = \frac{0.5}{50 \text{ K}16^2} = 330 \text{ KL}$

$R_4 = \frac{14 - 0.5}{50 \text{ K}16^2} = 30.3 \text{ KL}$

$R_5 = \frac{0.79}{4} = \frac{0.5}{13 \text{ K}16^4} = 30.3 \text{ KL}$

$C_1 = 0.3 \text{ uf}$

$t = \frac{1}{24} = \frac{1}{2 \times 400} = \frac{1}{800} = 1.25 \text{ mA}$

$J_1 = \frac{C_1 \text{ AM}}{4} = \frac{0.1 \times 10^6}{800 \text{ K}^2} = 80 \text{ UA}$

$R_1 = \frac{N_0 \text{ UTP}}{2_1} = \frac{17 - 0.5}{800 \text{ K}^2} = 206.21 \text{ KL}$

$S_1 = \frac{14 - 0.79}{50 \text{ K}16^2} = 270 \text{ KL}$

$C_1 = 14.003 \text{ Bmax} = 50 \text{ UA}$

$R_3 = 1603 \text{ Bmax} = 50 \text{ UA}$

$R_4 = \frac{14 - 0.5}{50 \text{ K}16^2} = 270 \text{ KL}$

$R_3 = 0.5 / (\text{K}0.6^2) = 10 \text{ KL}$

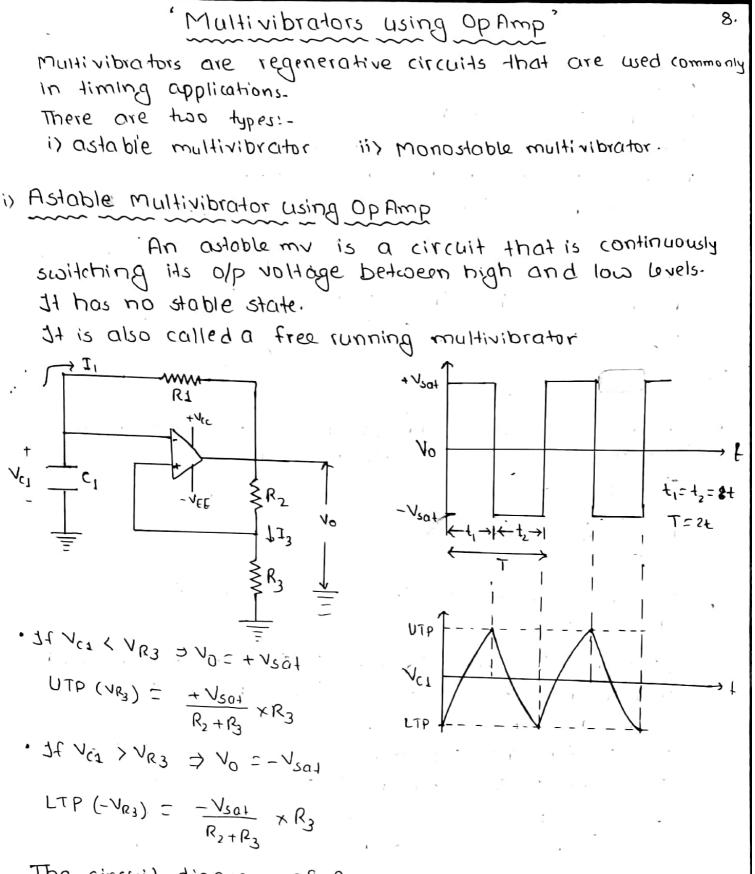

# Monostable Multivibrator

A mmv has one stable output state. Its normal O/p voltage may be low or high and it stays in the normal state until it is triggered. When a trigger i/p is applied, the output switches to its opposite state for a time dependent on the circuit components.

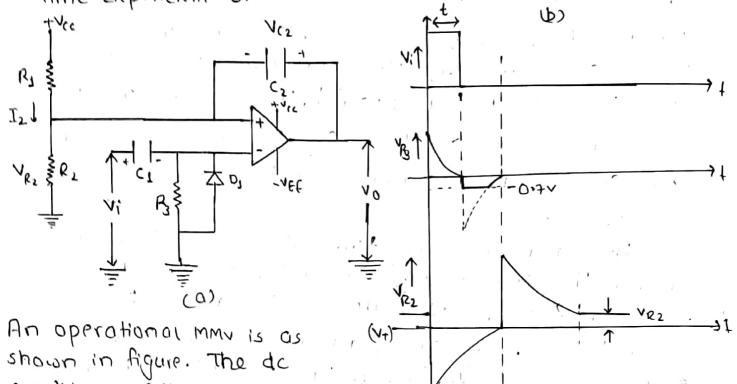

shown in figure. The dc conditions of the circuit are that the op-amp inverting i/p terminal is grounded via resistor R3 and the non-inverting i/p terminal is biased positively by resistors R1 and R2.  $V_{22}$   $(V_{t})$   $+V_{3at}$   $V_{0}$   $-V_{5at}$   $+V_{5at}$   $+V_{p}$   $+V_{p}$  $+V_{p}$

consequently, the op-omp is normally of the saturation & capacitor C2 is charged with the polarity shown.

An input pulse vi applied to C, is differentiated by R3& C1 to produce positive and -ve spikes (VR3) at the op-anp inverting i/p terminal as shown in figure (b).

The -ve spike is dipped of - 0.7 v by diode Di , so that it has no effect on the circuit.

The positive spike eips the inverting input terminol above the bias lovel of the non-inverting input and thus comes the Scanned with CamScanner Op-amp 0/p to scalitch to the -ve saturation level. The spike has a short time duration, so the inverting input terminal guickly returns to zero voltage level. However, when 1/p goes to -Vsat, the charge on  $C_2$  drives the non-inverting input voltage (Vt) down to  $V_1 = -V_{501} - V_{C_2}$

which is below the ground level. and this voltage is present of non-inverting i/p terminal even after the input triggering spike has disappeared, thus keeping o/p at -Vser.

with the olp at - Viat , C2 discharges via R, & R2, thus gradually raising non-inverting 1/p terminal towards ground lovel.

When non-inverting terminal goes slightly above ground, the op-amp o/p immedietly switches back to + vsat once again and the circuit is returned to its original state. The circuit produces a -ve going pulse each time it is triggered. The pw of o/p depends on C2, VR2 and R1 & R2.

Design:

- Let,  $J_2 = 100 J_{Bmax}$

- · Assume, VR2 = 0.5 V

$$R_2 = \frac{V_{R_2}}{I_2}$$

and  $R_1 = +\frac{V_{cc} - V_{R_2}}{I_2}$

$$R_3 = R_{max} = \frac{0.1 \, \text{V}_{BE}}{\text{J}_B \, \text{max}}$$

To generate spikes from 1/p pulse, the time constant signs should be approximately one-tenth of i/p pulse width.

C1 R3 = 0.1 t

$$\Rightarrow C_1 = \frac{O'1T}{R_3}$$

Scanned with CamScanner

- or, c1 might be selvated first much larger than stray capacitonce, then R3 can be calculated from the above equation.

- · To find (2,

consider the capacitor charging equation

$$e_{c} = E - [E - F_{0}] e^{-r/RC}$$

$$\Rightarrow \overline{e}^{1P/RC} = \frac{E - e_{c}}{(E - F_{0})}$$

$$- \frac{1}{P}R_{c} = \ln \left(\frac{E - e_{c}}{E - F_{0}}\right)$$

$$\frac{1}{P} = RC \ln \left[\frac{E - F_{0}}{E - e_{c}}\right]$$

$$At = pw, C = C_{2} \otimes R = R_{1} \prod R_{2}$$

$$\frac{1}{P} = (R_{1} \prod R_{2}) C_{2} \ln \left[\frac{E - F_{0}}{E - e_{c}}\right]$$

$$C_{2} = \frac{1}{(R_{1} \prod R_{2})} \ln \left[\frac{E - F_{0}}{E - e_{c}}\right]$$

$$\frac{1}{P} \Rightarrow pulse width (pw)$$

E → Capacitor charging voltage that is the voltage that it would charge to after triggering if it were allowed to continue charging without the olp switching from -Vsa.

$$\therefore E = v_{R_2} - (-v_{sat})$$

Es → Es is the initial capacitor voltage before triggering Taking E as a the quantity, Es must be assigned a -ve polority.

$$E_0 = - \left[ + N_{sof} - N_{R_2} \right] = N_{R_2} - \left( + N_{sof} \right)$$

17.

$$e_{c} \rightarrow e_{c} \text{ is the final capacitor voltage at which op-orap

autput scatches from -Vsat to +Vsat. This is the voltage

arrows c, when the non-inverting the terminal is at

Bround level and the old is still at -Vsat.

$$e_{c} = 0 - (-Vsat)$$

$$e_{c} = +Vsat$$

A: Design a MMV to have an old pulse width of 1ms when

triggered by a 2v, 100 us input pulse. Use 741 op amp with

t try supply.

Sol<sup>M1</sup> Let,  $J_{2} = 100 \text{ tB max} = 50 \text{ uR}$

$$w_{1} V_{R2} < V_{1}$$

$$V_{R2} = 0.5v$$

$$R_{2} = \frac{V_{R2}}{J_{2}} = 10 \text{ tr (sid volue)}$$

$$R_{1} = \frac{V(c - V_{R2})}{J_{2}} = 230 \text{ kn} \approx 220 \text{ kn}$$

$$e_{c} = +V_{sat} = (12 - 1) = 11 \text{ v}^{1}$$

$$c_{2} = \frac{1p}{(P_{1} + P_{2}) \ln (\frac{E-E_{0}}{E-E_{0}})} = 0.027 \text{ uf } \approx 0.03 \text{ uF}$$

$$R_{3}(max) = 140 \text{ kn} \approx 120 \text{ kn}$$$$

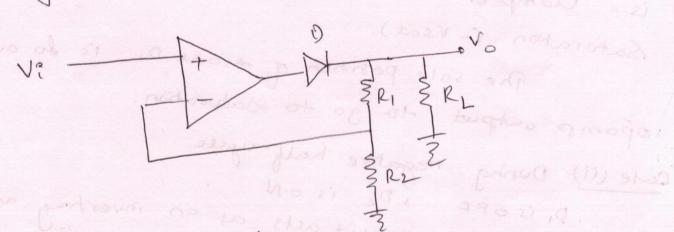

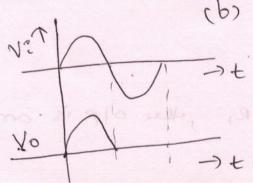

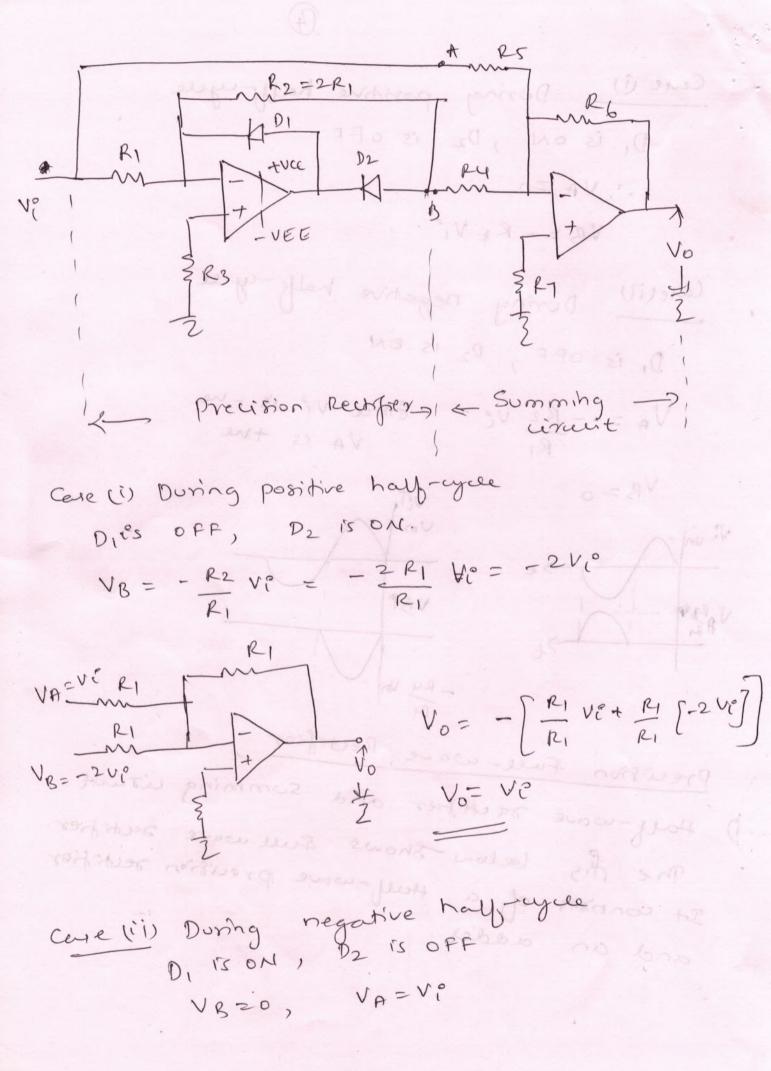

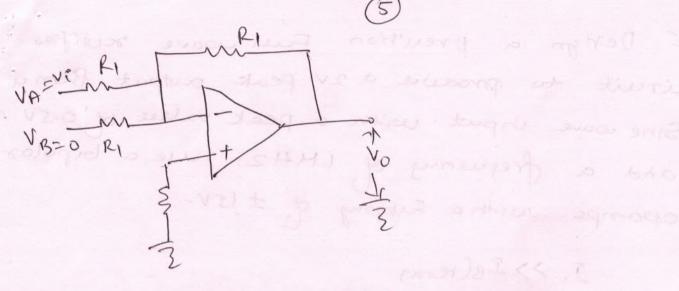

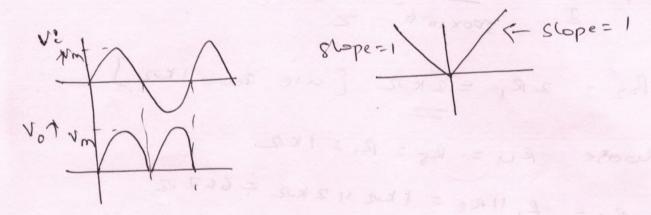

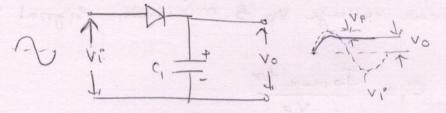

Oself 2 and a second Precision Hauf-wave circuits \* Saturating precision Rectifier The circuit of an op-amp precision scitzier is shown in fig. It is simply a voltage follower with a diode connected between the op-amp olp Terminal and see circuit output point.  $\frac{V_{i}}{A} = \frac{1}{2} \frac{1}{2$ Care (1): During positive Half-yque Diode Diis and. The feedback parts is boolyon. The worsent through RL is zero. 1. Vozo. Case (i) : During positive Half-agree Diode D, is ON. and op-amp circuit acts as voltage Follower. Vo=V? Care (ii) : During regative half youe D, is off. Me feelback path is proken. Me wrocht through RL is Zero. ... Vo=0.

Noti- Orainary Rectifiers uning Si avodes have a cut-in Voltage of 0.7V. Hence the rectification of Sinusoidal Signal starts above only above the unt-in Voltage V.F. Below V.S rectification is not possible. In prevision Rectifier, sectification below V.F is possible.

In the above fig, doning negative half-eyele didde D is OFF, and op-amp operates in open loop. Open loop vottage gain of opampis Very high and output of opamp goes to -Vsat. This limits the frequency suppose of the virtuit. For high frequency application, a non-saturating prevision rectifier must be med.

The fig bleow shows the prevision securifier with voltage gain. This is a non-inverting amplifier with dibde inluded. The virtuit is designed as non-inverting amplifier. Me Mihimum corsent through R, and R2 should be a minimum of 100 leasts ensure dibde is operating correctly. A minimum of SDOLLA 13 a good derign. lo sept als

when D is ON,  $V_0 = (1 + \frac{R_1}{R_2}) V_i^2$

(2)

If the polarities of D, and D2 are Reversed, positive half yell will be reinfied with invertion and regative half yell is dipped.

Derign The inverting amplifier is derigned first. The reverse break down volkage of diace mult the reverse break down volkage. The diade be greater than the supply voltage. The diade be greater than the supply voltage. The diade he greater than the supply voltage of the much smaller Reverse receivery time mult be much signal then the time periods of the highest signal frequency to be proceed. frequency to be proceed.

En: - Design a Mon-saturating precision the of shown above to produce a 2V peak autput from a sine wave "Ip with a peak value of 0-5V and frequency of IMHZ. We a bipolar op-amp with a supply of ±15V. let I, >> IBrean

$T_{1} = Svoup$   $F_{1} = \frac{0.5}{I_{1}} = \frac{0.5}{500 \times 10^{-6}} = R_{1} \ge 1 k R_{2}$

$$f_{ain} \frac{v_0}{v_i} = \frac{2}{0.5} = 4,$$

$$\frac{R_2}{R_1} = 4$$

$$\therefore R_2 = 4 R_1 = 4 Kn$$

$$R_2 = 3 - 9 Kn + 8 Fol Value$$

$$K_{3} = K_{1} \# K_{2}$$

$$= 1 K \# 39 K = 796 n$$

We  $R_{3} = 820 \text{ all}$

The break down Voltage of Di and D<sub>2</sub>

Should be 30V (15 - (-15V))

$$t_{37} < T, \quad T = \frac{1}{10} = 1.415$$

$$t_{37} < T, \quad T = \frac{1}{10} = 0.1415$$

$$The fis below shows two output previous

The fis below shows two output previous

$$K_{2} = \frac{K_{2}}{V_{3}}$$

$$K_{3} = \frac{V_{3}}{V_{3}}$$$$

the sevence break down

sold in the for the former to see

when Rois greater than Ry and R5 not Noie only sectification but amplification is possible. A prevision fue ware section is also could as an absoult value count.

En: Derign a preution Fuel wave scarper circuit to produce a 2V peak output from a Sine some input with a peak valee of 0.5V and a frequency of IMHZ. We a bipolas opamps with a supply of ± 15V.

I. >> IB(Hen)

let I, = sooleA (for adequate diode wrokent)

A previous free

no po hered

$$R_1 = \frac{V_1}{Z_1} = \frac{0.5}{500 \times 10^{-6}} = 1 k n$$

Choose Ry = 25 = R, = 1K2

we k3 = 680 2

$$V_{0} = \frac{R_{6}}{R_{1}} \frac{V_{0}}{V_{1}^{2}} = \frac{R_{6}}{R_{1}} = \frac{2}{0.5} = \frac{2}{K_{1}}$$

Ry = Ry 11R5 11R6 = 1 K211 1 Kun 11 3.9 Kul = 44302

For diade, D, and D2 the severe breakdown

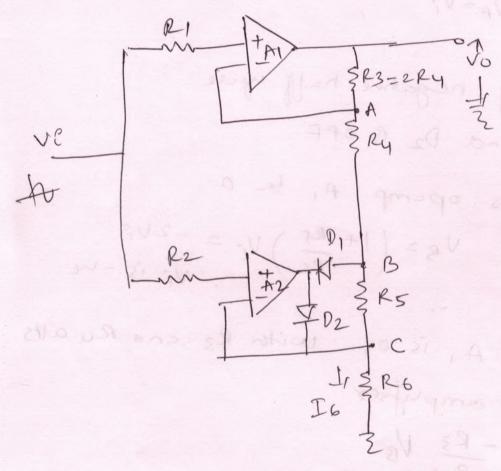

op-amp A, with Rg and Ry and opamp A2 with Rs and R6 compitute two non-inventing amplifiers. However diody P, and D2 affect operation of the amuit. the cere(i) During positive half-yre D2 IS ON and D, is OFF.

Opamp A2 aus as voltage follower -i. Vo= Ve

Since there is no potential difference between A and C, no writert flows through R3. ... drop across R3 is D.

19

$$V_0 = V_A = V_i^2$$

when  $elp to A_1$  is o, with  $R_3$  and  $R_4$  alts as chreating amplifier  $V_0 = -\frac{R_3}{R_4} V_B$

$$\begin{array}{c} \gamma f R_3 = 2R_4, V_0 = -2V_B \\ V_0 = -2(-2V_P) = 4V_P \\ \end{array}$$

By Superposition theory

$$V_{0}$$

= + 4  $V_{1}$  -  $3V_{1}$  =  $V_{1}$

$V_{0}$  =  $V_{1}$

Hence the above vicuit works of furnish

suffred with high  $J_{p}$  impedance.

Delign  $R_{6}$  is calculated first,

Men  $R_{4}$  =  $R_{5}$  =  $R_{6}$ ,  $R_{3}$  =  $2R_{4}$

Entry Uping Bipolar opamp with  $V_{16}$  =  $\pm 15V$ ,

derign the high input impedance prevision

fund - wave such first within the input peak

Nothage is to be IV and no am putation

to owner.

(et  $T_{6}$  =  $500 \text{ MA}$

$R_{6}$  =  $\frac{V_{1}}{T_{6}}$  =  $2kR$

$R_{4}$  =  $R_{5}$  =  $R_{6}$  =  $1.8 \text{ km}$ ,  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ),  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ).  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ).  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ).  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ).  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ).  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$R_{1}$  =  $R_{2}$  (IR<sub>4</sub> =  $3.6 \text{ km}$ ).  $R_{3}$  =  $2R_{4}$  =  $3.6 \text{ km}$

$$R_2 = R_5 \parallel R_6 = 1.8 \parallel 1.8 \parallel = 900 n$$

wel  $R_2 = 1 \mbox{ box } 844 \mbox{ Value }.$

Limiting circuits

peak clipper Way w

The fig below shows the viruit of a Peak dipper voluee back to back zerve airdy are used to dip the peaks of the inputs at the output. One divide is forward biased (vd) the output. One divide is forward biased (vd) and the other is driven into breakdown (v2), and the other is driven into breakdown (v2), when due olp voltage is greete then (vot v2) the olp cannot exceed ± (vot v2). the olp cannot exceed ± (vot v2). the olp cannot exceed ± (vot v2). the olp cannot exceed ± (vot v2).

$$\frac{1}{2} R_3 \qquad \frac{1}{2} - (v_2 + v_0) + \cdots + \frac{1}{2}$$

As long as [Vo] < (V2+VD], the visurit behaves as a inverting amplifier. This type of virurit is used to protect a duvice that might be damaged by excertive input voltage. The fig us shows a refistor Ry connected The fig us shows a refistor Ry connected in series with R1 so that output himiting voltage Gn be adjusted. Zener dibays are connected to the moving contact of Ry.

AS = 1.47KIIISE = ANZA

Defign: Zener diodeg are selected to limit the output Voltage at the derived level with Vo=0.7V. Me Enverting amplifier is designed to produce the derived Voltage gal.

when the ofp reaches the limiting bree worsent flowing through R1, part of it flows through R2 and part through Zenor diodus,

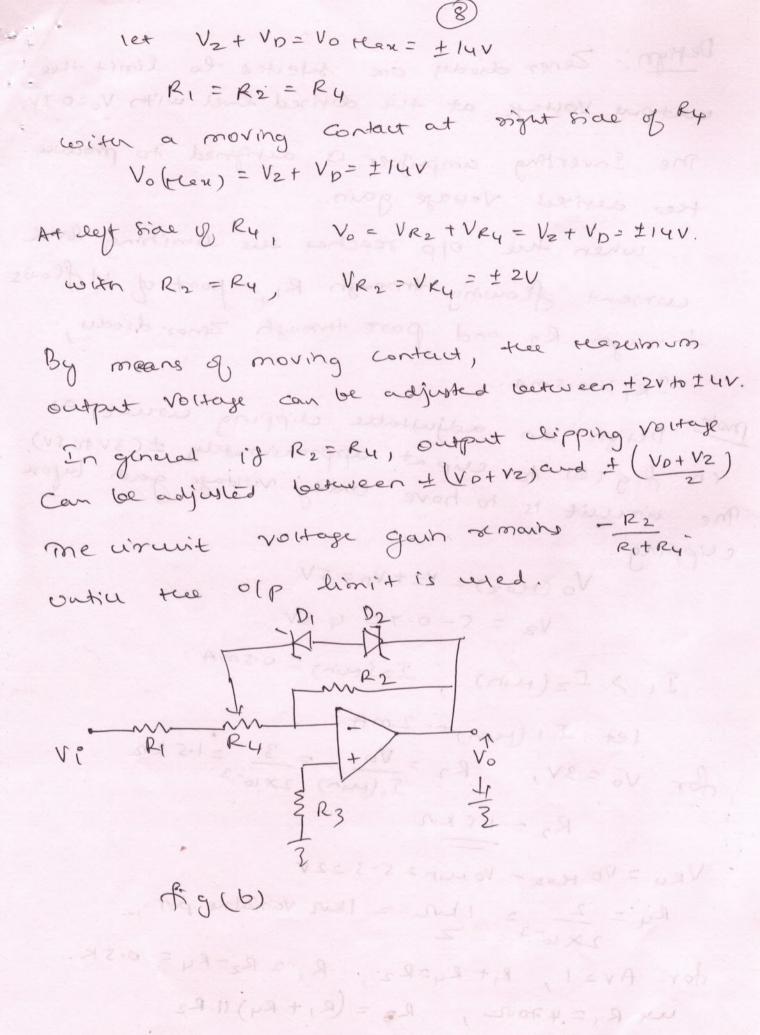

Mob Derign an adjustable clipping viruit as in fig (6) to clip at approximately ±(3vtosv). The vircuit is to have Unity voldage grain before The vircuit is to have Unity voldage grain before

$$V_{0} (Hex) = V_{2} + V_{0} = SV$$

$$V_{2} = S - 0.7 = 4.3V.$$

$$I_{1} > F_{2}(Hun), \quad J_{2}(Hun) = 0.5 \text{ mA}.$$

$$Iet = J_{1}(Hun) = 2 \text{ mA}.$$

$$for \quad V_{0} = 3V, \quad R_{2} = \frac{V_{0}}{I_{1}(Hun)} = \frac{3}{2 \times 10^{-3}} = 1.5 \text{ kg}.$$

$$R_{2} = 1.5 \text{ kg}.$$

$$V_{Ry} = V_{0} Hex - V_{0} \text{ min}^{2} S^{-3} = 2V.$$

$$R_{ij} = \frac{2}{2 \times 10^{-3}} = 1 \text{ km} = 1 \text{ km} \text{ variable pot}.$$

$2 \times 10^{-3} = 2$

$R_{ij} = R_{2} - R_{ij} = 0.5 \text{ km}$

for

$$Av_{21}$$

,  $k_{1} + k_{4} = R_{2}$ ,  $R_{1} = R_{2} - K_{4}$

$w_{1} R_{1} = 470 \Omega$ ,  $R_{3} = (R_{1} + R_{4}) \parallel R_{2}$

$R_{3} = 1.47 \text{K} \parallel 1.5 \text{K} = 742 \Omega$

$w_{1} R_{3} = 680 \Omega$

Dead Zone virwit A dead zone virwit can be obtained de reference Voltage by adding a visitor R, and a de reference voltage Vset to hay -wave precision sectsifier. This is shown in Es below. Vse k2 Vse k2 Vi k2 Vi k2 Vi Vo Vo Ry iff R, and Very wree absent, the interit behaves as an inverted half-wave precision xetsfier. If dibdes were absent CD, OFF, D2 ON) the circuit behaves as an inverting summing viscit output q vo=- (vxy+vi) (i) let Vzy be positive when Vizo, Volis-ve ... D. ISDAI and Vozo D2 ISOFF. when Vi goes-ve and goes just below - Viry Vol becomes tre, co that D, is OFF P2 is ONI. ie F Vi) = [+ Vsey], Vo=0 and 0/P, Vo=-(Vsey+Vi) Since V? is -ve, Vo= - v zey + Vio

Perturning a BSFET opermit earling a dead zone

where the parts only the upper IV portion of the

point the hard-agae of the sine wave CIP with

a peak value of SV.

Nay = Vo-1 = 3-1 = 2V.

IR, buin = Ichnin = COOMA

IR, R = 2

R\_1 =

$$\frac{2}{500,700}$$

= 4K, where  $R_1 = 3.9KR$ .

$R_1 = K_2 = F_2 = 3.9KR$

$R_1 = K_2 = F_2 = 3.9KR$

$R_2 = R_1 IIR_2 II R_2 = 3.9KR$  II 3.9K

$R_4 = 1.3KR$  we  $R_4 = 1.2KR$

$R_4 = 1.3KR$  we  $R_4 = 1.2KR$

$R_4 = 1.3KR$  we  $R_4 = 1.2KR$

$R_5$  The old of dead zone aluse

is applied to an inverting commits

(termined B). The old Vi cs applied at termined

$A$  of the Summing is wit.

$A$  of the Summing is wit.

$A$  of the Summing is wit.

$R_7$   $R_7$

(10)

A man

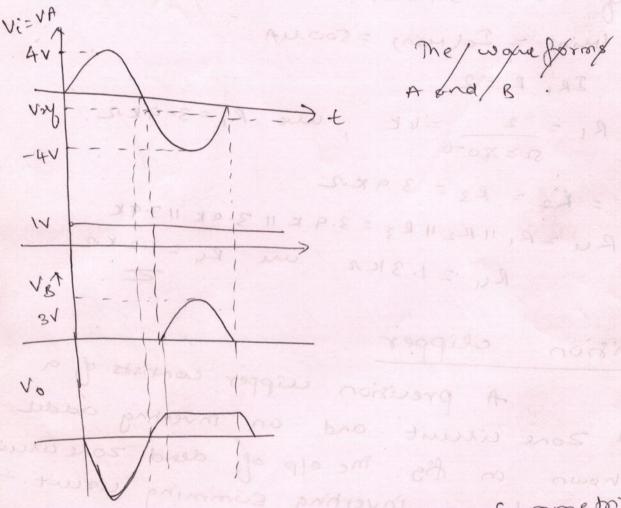

The waveforms at lerminaly A and B soutant. Olp Vo is shown. The olp is inverted ilp wif with the positive plat previsely hipped off above the lurel of Vref. 2 pour they a

The worke forms of terminal A and B.

Vo Vo Shows the syrorretorical contrists of the me fig below shows the syronoetrical prevision cripping circuit. It consists of two clead zone circuits with a 31/p inverting adder. One clead zone circuit has the reference and other circuit have -ve reference Voltage with the diodes seversed. When the waveform at terminal A, B and c are summed and inverted, the olp is an inverted vertion of Vie with the both peaks previsely clipped at the

\* clamping circuits

Diode clamping circuit

A clamping viruit reproduces an input waveform without any clipping or distortion, but limits the upper or lower peak of the waveform to a predetermined level.

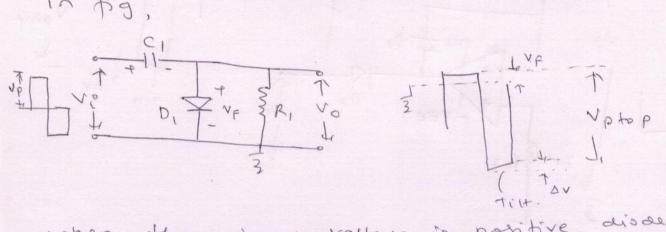

Consider the diode clamping circuit shown in fig,

when the input voltage is positive, disae D, is forward-biased and capacitor C, changes with the polonity shown.

The peak input voltage (VP) appears across (, and D, fo the Capacitor charges to Vc, = Vp-Vp

At this time, the output voltage cannot exceed the voltage drop across the forward braged didde.

when the input goes to its negative peak, D, 13. Averse brased and input and capacitor Voltages Combine to produce an output of

$$V_0 = -V_P - V_{C}(V_0 = -V_P - (V_P - V_P))$$

$$V_0 = -2V_P + V_F$$

The Rehistor R, is used to ensure the capacitor discharges when the peak input Voltage drops to a lower level. R, produces tilt (or slope) on the Undamped peak of the output.

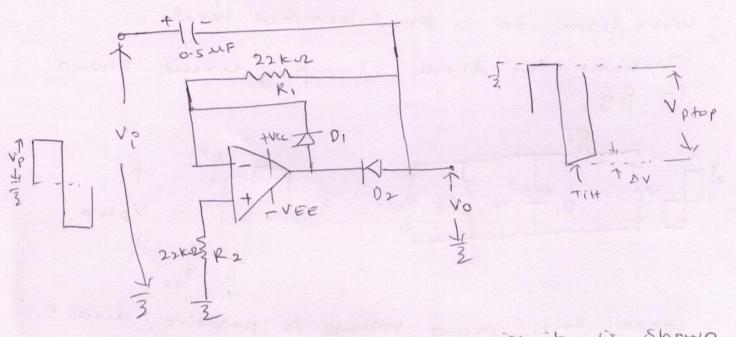

precision clamping circuit.

The precision clamping circuit is shown above.

when the input voltage is at tVp, the viruit Output tends to more in positive direction. Thus, because the op-amp inverting input is connected to the output by repistor R, the inverting input to the output by repistor R, the inverting input termined tends to be pointive with respect to termined tends to be pointive with respect to the grounded non-inverting input terminal. This the grounded non-inverting input terminal. This causes the op-amp output to go negative, serviting causes the op-amp output to go negative, serviting to diode D<sub>2</sub> being forward bicged and diode D, being reverse brased. Allegative feedback via R, keeps the inverting input terminal and the anode 2 D<sub>2</sub> within serv & ground level. The output voltage at this time is

Vo=0.

when the input goes to its negative peak, the circuit output and the op-amp inverting input terminal tend to go negative. The Negative Voltage at the inverting input causes the op-amp output terminal to move in positive direction, versching  $D_2$  & forward biasing  $D_1$ . Now, negative reversing  $D_2$  & forward biasing  $D_1$ . Now, negative feedback via  $D_1$  keeps the op-amp inverting input terminal close to the level of the input terminal close to the level of the grounded mon-investing input terminal. with  $D_2$ grounded mon-investing input terminal. with  $D_2$ free to move in a negative direction, giving

the output &,

$V_0 = V_1 + V_q$  $V_0 = -V_p + (-V_p)$  $V_0 = -2V_p.$

Reversing the polarity 2 D, and D2 produces Champing 2 the lower level 2 the output waveform.

In any clamping write, the signal source resistance Rs is in series with the capacitor when it is charging, Allowing that the capacitor should be completely charged from zero to Vp in five cycles & i/p waveform,

$$C_{i} = \frac{T}{2Rs} = \frac{1}{2Rsf}$$

when C<sub>1</sub> is discharging Via R<sub>1</sub>, the Voltage across R<sub>1</sub> is

giving a discharge worsent of

$$I = \frac{2 V P}{R_1}$$

and  $C_1 = \frac{Q}{\Delta V} = \frac{\Gamma E}{\Delta V}$

where AV is the discharge voltage, or tilt, on the unclamped peak and t is the discharge time T12.

$$C_{1} = \frac{2VP}{R_{1}} \times \frac{T}{2} \times \frac{1}{\Delta V}$$

$$R_{1} = \frac{VP}{C_{1}\Delta V f}.$$

prob A ± sv, 10 KH2 Square wave form a signal Source with a schistance & 100 2 is to have its positive peak clamped precisely at ground level. Tilt on the output is not to exceed 1.1. 2 Peak amplitude & wave. Design a suitable op-amp precision clamping circuit with supply 2 ± 122.

$$C_{1} = \frac{1}{2R_{s}f} = \frac{1}{2 \times 100 \times 10 \times 10^{3}} = 0.5 \text{ MF} (std).$$

$$A_{V} = \frac{1}{2} \sqrt{9} \text{ SV} = 0.05 \text{ V}$$

$$R_{1} = \frac{VP}{C_{1} \text{ AV}f} = 20 \text{ K} \sqrt{2} = 22 \text{ K} \sqrt{2}.$$

$$R_{1} = R_{2} = 22 \text{ K} \sqrt{2}.$$

$$T = \frac{1}{2} \sqrt{2} \text{ K} \sqrt{2}.$$

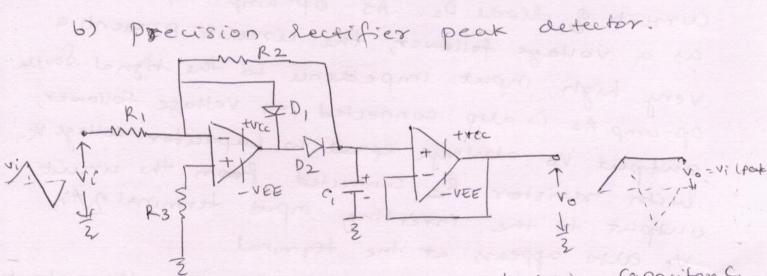

Peak Detectors : A peak detector monitors an input signal and holds its output voltage at the peak level of the input.

a) Simple diode capacitor peak detector.

when the input voltage increases to Vp, the Capacitor is charged to (Vp-Vp). when Vi falls below Vp, D, is severe biased and C, retains its charge. The drawback of the above circuit is

that the diode voisage drop introduces Considerable error.

On the above circuit holding capacitor G is charged via low-output resistance of op-ampth. By making relistor Rz greater than R, the Rignal may be amplified as well as peak Rignal may be amplified as well as peak detected. op-amp Az connected as Voltage-Follower

(3)

isolates the capacitor from the discharging effect of any load repistance. WRT  $C = \frac{Q}{V} = \frac{St}{V} = \frac{Id}{AV}$   $C_1 = \frac{Id}{AV}$   $C_1 = \frac{Id}{AV}$   $C_1 = \frac{Id}{AV}$   $C_2 = \frac{St}{V}$   $C_1 = \frac{Id}{AV}$   $C_2 = \frac{St}{V}$   $C_1 = \frac{St}{AV}$   $C_2 = \frac{St}{AV}$   $C_2 = \frac{St}{AV}$   $C_2 = \frac{St}{AV}$   $C_3 = \frac{St}{AV}$   $C_4 = \frac{St}{AV}$   $C_5 = \frac{St}{AV}$  $C_5 = \frac{$

For a peak voltage vp & minimum signal size time tr,

$$To reax = \frac{C_1 V P}{tr}$$

, ruin. slew rate =  $3 \frac{V P}{tr}$

Voltage Follower peak detector In the previous wruit, the only Capacitor discharge wrents are the input biss wrent to op-amp A2 and severe leakage wrent of diode D2. As op-amp A, is connected as a voltage follower, the viruit presents a very high input impedence to the bignal Source. Very high input impedence to the bignal Source. op-omp A2 is also connected as voltage follower, op-omp A2 is also connected as voltage follower, output vo always equal to capacitor voltage Vc. output vo always equal to capacitor voltage Vc. output to the inverting input terminal of A1, Ve also appears at the terminal.

when vi is greater than Vc, the output & A; is positive, D2 is forward brased and A; behaves as a voltage Follower, charging C; to Vp. when ve falls below Vp, Vc semains at Vp, s consequently, the inverting input terminal of A; also semains at Vp. ... the output of op-amp A, goes negative, sevening D2 and forward biahing D1. Negative fledback Vid D, keeps A, Room going into Saturation.

prob : Destign Voltage follower peak detector with the pulse-type signal Voltage has a peak value approximately 2.5V with a rise time 2 5 us, and ofp Voltage is to be held at 2.5V for a time 3 loo us. The maximum output error is to be approximately 1%. Calculate output error is to be approximately 1%. Calculate the required component Values and Specify the ofp correct and Siew rate 3 op-amp.

-> use BIFET op-amps for mini capacitor

leokage wrocht.

let R<sub>1</sub> = R<sub>2</sub> = 1MD

C<sub>1</sub> discharge wrocht, Id DIr(D<sub>2</sub>) = 1MA

$$\Delta v = 1/2, 2/p = 1/2, 2.5 = 25mv$$

C = Id th = 4000 pf. (std)

For opamp AI,

$$Jocman = \frac{C_1 VP}{t_8} = \frac{4000PF \times 25V}{5us}$$

= 2 mA.

min. Slew sale = 3 VP = 1.5 V/ey

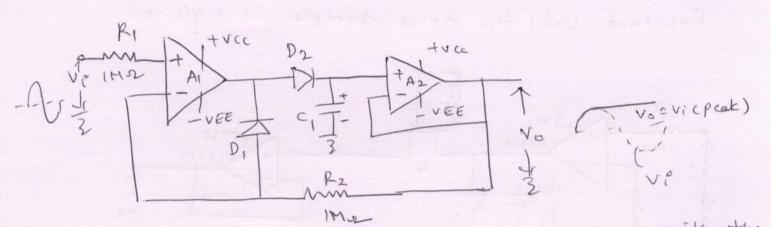

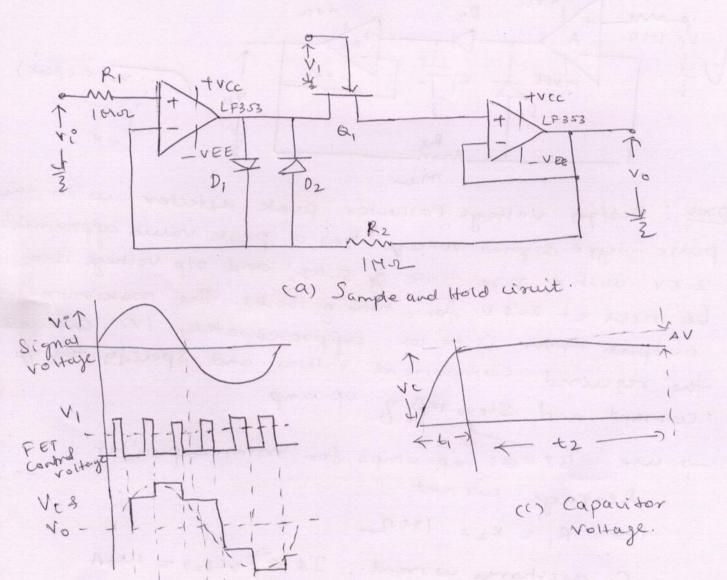

\* Sample and Hold circuits.

A Sample and Hold cirvit Samples amplitudes of a signal voltage at any point in its waveform and holds the voltage level Constant Until the next Sample is aquired.

(b) w1f

Q<sub>1</sub> is repeatedly switched ON and OFF by the pulse waveform (control voltage Vi) applied to its gate terminal. If input Vi becomes larger than capacitor voltage Vc while Q<sub>1</sub> is OFF, C<sub>1</sub> than Capacitor voltage Vc while Q<sub>1</sub> is OFF, C<sub>1</sub> rapidly charges to the level gVi when Q<sub>1</sub> swithey ON. If Vc is initially greater than Vi, G is

e, is discharged to the level of Vi when Q, 13 ON. when Q, is off, only the input bias consent to A2 and the FET gere - source severse leakage writent are effective in discharging the capacitos So, C, holds the Sampled Voltage Constant until the next sampling instant.

During the Sampling time or aquisition time, Ci is charged via the FET channel resistance Rocon, . If the Sampling time is ti= 5 c Rocon

the capacitor is charged to 0.993 of the input voitage, resulting in a 0.7% error in the Sample amplitude.

If t\_= TCRDCOND is used error is 0.14. During the holding time tz, the capacitor is partially discharged.

more se now preve shift is 180° when

maning there share an in